# ECM-I910 User's Manual

Ver.A1.2

Date: July 28, 2022

# **Version Note**

| No. | Ver. | Note                                                                                                                                          | Date       | Writer      | Check man |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-----------|

| 1   | A1.0 | first publish                                                                                                                                 | 2021.06.10 | Grace Xiong | Colin     |

| 2   | A1.0 | add the setting and programming instuctions of BIOS                                                                                           | 2021.06.08 | Grace Xiong | Colin     |

| 3   | A1.1 | Add installation steps                                                                                                                        | 2021.08.19 | Zhuozhi Li  | Colin     |

| 4   | A1.2 | <ol> <li>Change network chip type: replace two</li> <li>chips with a 219 chip and a 226 chip</li> <li>Replace ALC662VD with ALC897</li> </ol> | 2022.07.28 | Zeqi You    | Colin     |

|     |      |                                                                                                                                               |            |             |           |

|     |      |                                                                                                                                               |            |             |           |

|     |      |                                                                                                                                               |            |             |           |

|     |      |                                                                                                                                               |            |             |           |

|     |      |                                                                                                                                               |            |             |           |

|     |      |                                                                                                                                               |            |             |           |

### **Copyright**

The documentation and the software included with this product are copy- righted 2018 by Shenzhen JHC Technology Co., Ltd. All rights are reserved. Shenzhen JHC Technology Co., Ltd. reserves the right to make improvements in the products described in this manual at any time without notice. No part of this manual may be reproduced, copied, translated or transmitted in any form or by any means without the prior written permission of Shenzhen JHC Technology Co., Ltd. Information provided in this manual is intended to be accurate and reliable. However, Shenzhen JHC Technology Co., Ltd. assumes no responsibility for its use, nor for any infringements of the rights of third parties, which may result from its use.

### Acknowledgements

Award is a trademark of Award Software International, Inc.

IBM, PC/AT, PS/2 and VGA are trademarks of International Business Machines Corporation.

Intel, Celeron are trademarks of Intel Corporation.

Microsoft Windows and MS-DOS are registered trademarks of Microsoft Corp.

RTL is a trademark of Realtek Semi-Conductor Co., Ltd.

All other product names or trademarks are properties of their respective owners.

For more information on this and other JHC products, please visit our websites at: <a href="http://www.jhctech.com.cn">http://www.jhctech.com.cn</a>

### **Product Warranty (2 years)**

JHC warrants to you, the original purchaser, that each of its products will be free from defects in materials and workmanship for two years from the date of purchase.

This warranty does not apply to any products which have been repaired or altered by persons other than repair personnel authorized by JHC, or which have been subject to misuse, abuse, accident or improper installation.

JHC assumes no liability under the terms of this warranty as a consequence of such events.

Because of JHC.s high quality-control standards and rigorous testing, most of our customers never need to use our repair service. If an JHC product is defective, it will be repaired or replaced at no charge during the warranty period. For out-of-warranty repairs, you will be billed according to the cost of replacement materials, service time and freight. Please consult your dealer for more details.

If you think you have a defective product, follow these steps:

- 1. Collect all the information about the problem encountered. (For example, CPU speed, JHC products used, other hardware and software used, etc.) Note anything abnormal and list any onscreen messages you get when the problem occurs.

- 2. Call your dealer and describe the problem. Please have your manual, product, and any helpful information readily available.

- 3. If your product is diagnosed as defective, obtain an RMA (return merchandise authorization) number from your dealer. This allows us to process your return more quickly.

- 4. Carefully pack the defective product, a fully-completed Repair and Replacement Order Card and a photocopy proof of purchase date (such as your sales receipt) in a shippable container. A product returned without proof of the purchase date is not eligible for warranty service.

- 5. Write the RMA number visibly on the outside of the package and ship it prepaid to your dealer.

### **Declaration of Conformity**

### CE

This product has passed the CE test for environmental specifications when shielded cables are used for external wiring. We recommend the use of shielded cables. This kind of cable is available from JHC. Please contact your local supplier for ordering information. Test conditions for passing included the equipment being operated within an industrial enclosure. In order to protect the product from being damaged by ESD (Electrostatic Discharge) and EMI leakage, we strongly recommend the use of CE-compliant industrial enclosure products.

### **FCC Class B**

Note: This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

### **Technical Support and Assistance**

- Step 1. Visit the JHC web site at <a href="www.jhctech.com.cn">www.jhctech.com.cn</a> where you can find the latest information about the product.

- Step 2. Contact your distributor, sales representative, or JHC's customer service center for technical support if you need additional assistance. Please have the following information ready before you call:

- Product name and serial number

- Description of your peripheral attachments

- Description of your software (operating system, version, application software, etc.)

- A complete description of the problem

- The exact wording of any error messages

# **CONTENTS**

| Gener  | al Info  | ormation                                         | 1  |

|--------|----------|--------------------------------------------------|----|

| 1.1    | Introdu  | ıction                                           | 2  |

| 1.2    | Featur   | es                                               | 2  |

| 1.3    | Specifi  | cations                                          | 3  |

|        | 1.3.1    | General                                          | 3  |

|        | 1.3.2    | Display                                          | 3  |

|        | 1.3.3    | Ethernet                                         | 3  |

|        | 1.3.4    | Audio                                            | 3  |

|        | 1.3.5    | Power Consumption                                | 4  |

| 1.4    | Enviro   | nmental Specifications                           | 4  |

| 1.5    | Model    | Specification                                    | 4  |

| 1.6    | Mecha    | nical Specifications                             | 5  |

| Hardy  | vare I   | nstallation                                      | 7  |

| 2.1    | Introdu  | ıction                                           | 8  |

| 2.2    | Jumpe    | rs and Connectors                                | 8  |

| 2.3    | Board    | layout: Jumper/Switch and Connector Locations    | 9  |

| 2.4    | Jumpe    | rs and Switches Settings                         | 10 |

|        | 2.4.1 ]  | How to set jumpers and switches                  | 10 |

|        | 2.4.2    | COMS-Clear CMOS data                             | 11 |

|        | 2.4.3 \$ | SW1-Power on mode AT or ATX selection            | 11 |

|        | 2.4.4    | F-Panel eDP Power supply 12V/5V/3.3V Mode Select | 12 |

| 2.5    | Inst     | all                                              | 12 |

|        | 2.5.1    | Install the radiators                            | 12 |

| I/O In | trodu    | etion                                            | 15 |

| 3.1    | Introd   | ıction                                           | 16 |

| 3.2    | I/O Int  | roduction and Pin Assignments                    | 16 |

|             | 3.2.1 Ethernet port (LAN1/LA2)           | 16 |

|-------------|------------------------------------------|----|

|             | 3.2.2 USB Connectors (CN4/CN5/CN6)       | 16 |

|             | 3.2.3 HDMI port (HDMI1)                  | 17 |

|             | 3.2.4 EDP connector                      | 18 |

|             | 3.2.5 DP connector (DP)                  | 19 |

|             | 3.2.6 Power Input Connector (CN1)        | 19 |

|             | 3.2.7 CMOS battery connector (BAT1)      | 19 |

|             | 3.2.8 Reset connector (J_RST1)           | 20 |

|             | 3.2.9 Serial ATA1 (S_SATA1)              | 20 |

|             | 3.2.10 SATA power connector (P_SATA1)    | 21 |

|             | 3.2.11 Front PANEL(F_PANEL)              | 21 |

|             | 3.2.12 Serial port connector1/2 (COM1/2) | 21 |

|             | 3.2.14 COM3/4(RS232)                     | 22 |

|             | 3.2.15 8-bit DIO Connector (GPIO)        | 22 |

|             | 3.2.16 J_AUD                             | 23 |

|             | 3.2.17 SMBUS Connector (SMB1)            | 23 |

|             | 3.2.18 CPU_FAN1                          | 23 |

|             | 3.2.19 J_PANEL1                          | 24 |

|             | 3.2.20 J-BLK 5PIN                        | 24 |

|             | 3.2.21 M.2 E-Key                         | 24 |

|             | 3.2.22 1*Mini-PCle                       | 26 |

| BIOS        | Setup                                    | 28 |

| <b>4.</b> ] | 1 BIOS Description                       | 29 |

|             | 4.1.1 Entering the Setup Utility         | 29 |

| 4.2         | 2 BIOS parameter settings                | 30 |

|             | 4.2.1 BIOS Navigation Keys               | 31 |

|             | 4.2.2 Main Menu                          | 31 |

|             | 4.2.3 Advanced Menu                      | 32 |

|             | 4.2.4 Chipset Menu                       | 42 |

|             |                                          |    |

| 4.2.5 Boot Menu       |       | 45 |

|-----------------------|-------|----|

| 4.2.6 Security Menu   |       | 47 |

| 4.2.7 Save & Exit Men | nu    | 48 |

| 4.3 Updating the BIOS |       | 48 |

| SYSTEM RESOURCE.      | ••••• | 50 |

| 5.1 WDT and GPIO      |       | 51 |

| 5.1.1 WDT             |       | 51 |

| 5.1.2 GPIO            |       | 51 |

# **General Information**

1

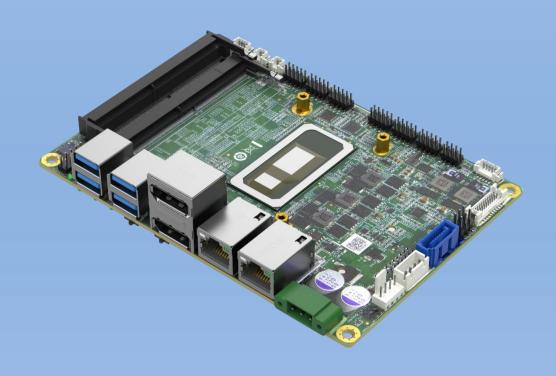

### 1.1 Introduction

ECM-I910 is powered by the Intel® Whiskey lake U CPU 2.2-4.6GHz, 4 cores 8threads. The motherboard supports DDR4 SO DIMM 2400MHz memory, up to 32GB. It features gen.9th Intel® UHD Graphics. ECM-I910 offers 1\*HDMI, 1\*DP, 1\*eDP, 2\*GbE LANs, 4\*USB3.0, 2\*USB2.0, 4\*COM, 8-bit DIO, 1\*M.2 2230 E-Key which supports WiFi 6/BT5.0, 1\*F-Mini PCIe with SIM slot support Mini PCIe and mSATA signal which can set by BIOS, supports 4G LTE module, 1\*SATA3.0 HDD/SSD are used for storage. DC 12V power input.

ECM-I910 also can support 9-36V wide power input through by one 75W power board OFX-075. This 3.5 inch Main board have compact size, complete function, easy to customize for embedded system applications, Very suitable for ITS, AI edge computing, intelligent manufacturing, intelligent security and other fields.

### 1.2 Features

### **Key Features**

- Intel<sup>®</sup> Whiskey lake U CPU 2.2-4.6GHz, 4 cores 8threads

- 2\*SODIMM, support DDR4 2400MHz, up to 32GB

- 1\*F-mini PCIe with SIM slot, can be set to Mini PCIe or mSATA by BIOS, support 4G LTE

- 1\*M.2 2230 E-Key, support WiFi 6/BT5.0

- 1\*SATA HDD/SSD bay, 1\*Msata(Optional) for storage

- 1\*eDP, 1\*HDMI, 1\*DP, support 3 independent display

- Optional Realtek ALC897 controller, supports 5.1 channel

- 1\*Intel® I226V, 10M/100M/1000M self-adaptive, support WOL Remote Wakeup 1\*Intel® I219LM, 10/100/1000Mbps self-adaptive, support WOL Remote Wakeup

- 8-bit DIO(1x2\*5pin header, 4\*USB3.0 gen1.0 type A, support max 5Gbps, 2USB2.0 (2x2\*4pin header), 4\*COM(4x2\*5pin header 2\*RS232/422/485, 2\*RS232), optional support TPM2.0

- Windows 10 IoT enterprise, Andriod, Ubuntu, Suse, Red Hat enterprise, Wind River Vxworks 7,

Yocto

- DC 12V power input, optional support 9-36V wide power input through by one 75W power board OFX-075, have 3\* CPU working status LED.

- AT/ATX pins are facilitate the setting of power-on mode. CMOS data pins are to facilitate the user to

clear CMOS operation

# 1.3 Specifications

### 1.3.1 General

CPU: Intel® Whiskey lake U CPU 2.2-4.6GHz, 4 cores 8threads

System chipset: Intel® Soc

**BIOS:** 128M-bit AMI EFI BIOS

**System Memory:** 2\*DDR4 2400MHz SODIMM, Up to 32GB **Watchdog Timer:** 255-level interval timer, setup by software

Serial Ports: 2\*RS232/422/485 2x2\*5 pin header, 2\*RS232 2x2\*5pin header

USB: 4\*USB 3.0 Type A ports, 2\*USB2.0 2\*4pin header,

**COM:** 2\*RS-232/422/485 2\*5pin DB header, 2\*RS232 2\*5pin DB header

GPIO: 8bit GPIO 2\*5pin header

### **Expansion Interface:**

1\*Full size Mini PCIe (PCIex1+USB+mSATA signal) with SIM slot

1\* M.2 2230 E-key · support WiFi6/BT5.0

**Storage:**1\*mSATA(Optional)

1\*SATA3.0 HDD/SSD

### 1.3.2 Display

Chipset: Gen. 9th Intel® UHD Graphics

**Display Memory:** Shared system memory

Resolution: HDMI 4096\*2304@24Hz; eDP 4096x2304@60Hz; 1\*DP 4096\*2304@60Hz

### 1.3.3 Ethernet

Chipset: 1\*Intel® I226V and 1\* Intel® I219LM Ethernet controllers

Speed: 10/100/1000 Mbps Integrated

**Interface:** 2\*RJ45

### **1.3.4** Audio

**Chipset:** Realtek ALC897 controller

**Interface:** 2\*5pin header

# 1.3.5 Power Consumption

Input Voltage: DC 12V Input, optional support 9-36V wide power input through by one 75W power

board OFX-075

**Power Consumption:** 19.92W (I5-8265U, 8GB DDR, 1\*500G SSD)

Power Adapter: AC to DC 12V/5A, 60W

# 1.4 Environmental Specifications

**Operating temperature:** -0~ 60° C

Relative humidity: 10~90% @ 40°C (non-condensing)

**Storage temperature:**  $-40 \sim 85$ °C ( $-40 \sim 185$ °F)

**EMC:** CE, FCC Class B

# 1.5 Model Specification

| Model NO.     | Introduction                                                                                                                                                                                     |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ECM-I910/S001 | 3.5"Embedded Single Board Computer, Intel® Core I3-8145U, 2*SODIMM DDR4, 2*LAN, 4*USB3.0, 2*USB2.0, 1*M.2, 1* Full size mini PCIe, 4*COM, 1*DP, 1*HDMI, 1*eDP, Mic & Line out, 1*SATA3.0, DC 12V |

| ECM-I910/S002 | 3.5"Embedded Single Board Computer, Intel® Core I5-8265U, 2*SODIMM DDR4, 2*LAN, 4*USB3.0, 2*USB2.0, 1*M.2, 1* Full size mini PCIe, 4*COM, 1*DP, 1*HDMI, 1*eDP, Mic & Line out, 1*SATA3.0, DC 12V |

| ECM-I910/S003 | 3.5"Embedded Single Board Computer, Intel® Core I7-8565U, 2*SODIMM DDR4, 2*LAN, 4*USB3.0, 2*USB2.0, 1*M.2, 1* Full size mini PCIe, 4*COM, 1*DP, 1*HDMI, 1*eDP, Mic & Line out, 1*SATA3.0, DC 12V |

| ECM-I910/S004 | 3.5"Embedded Single Board Computer, Intel® Celeron 4305U, 2*SODIMM DDR4, 2*LAN, 4*USB3.0, 2*USB2.0, 1*M.2, 1* Full size mini PCIe, 4*COM, 1*DP, 1*HDMI, 1*eDP, Mic & Line out, 1*SATA3.0, DC 12V |

| OFX-075       | 75W power board, DC IN 9-36V, DC OUT 12V, 38*53mm, TDP mini 54W, max 78W                                                                                                                         |

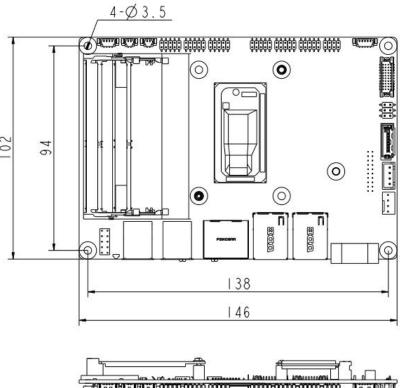

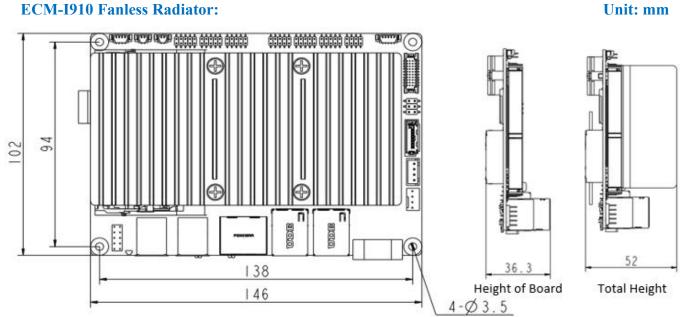

Unit: mm

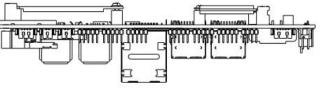

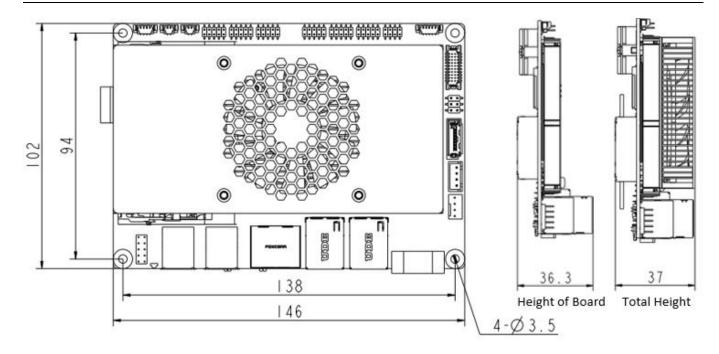

# **1.6 Mechanical Specifications**

### **ECM-I910 Dimension:**

Figure 1.1

### **ECM-I910 Radiator with Fan:**

**Unit: mm**

### **ECM-I910 Fanless Radiator:**

# **Hardware Installation**

# 2.1 Introduction

The following sections show the internal jumper/switch settings and the external connectors and pin assignments for applications.

# 2.2 Jumpers and Connectors

You can configure your ECM-I910 to match the needs of your application by setting the jumpers or switches.

The tables below list the function of each of the board jumpers and connectors. Later sections in this chapter give instructions on setting jumpers.

| Table 2.1: Switches and Jumpers                     |  |  |

|-----------------------------------------------------|--|--|

| Label Function                                      |  |  |

| ATX_AT Set Power-on mode at AT or ATX               |  |  |

| CMOS/CLR Clear CMOS Data Setting                    |  |  |

| J_PANEL1 eDP screen 3.3V/5V/12V Power supply Select |  |  |

| Table 2.2: Function interface |                                 |  |  |

|-------------------------------|---------------------------------|--|--|

| Label                         | Function                        |  |  |

| JPOWER1                       | DC Power connector              |  |  |

| SIM2                          | SIM card connector              |  |  |

| HDMI_B1                       | HDMI connector                  |  |  |

| DP                            | DP connector                    |  |  |

| EDP                           | EDP connector                   |  |  |

| J6                            | 2*USB3.11/2 connector           |  |  |

| J3                            | 2*USB3.13/4 connector           |  |  |

| LAN1                          | 1*LAN connector                 |  |  |

| LAN2                          | 1*LAN connector                 |  |  |

| J_USB                         | 2*USB2.0 2*4 pin header         |  |  |

| J_GPIO                        | 2*GPIO 2*5 pin header           |  |  |

| COM12                         | 2*RS232/422/485 2*5 pin header  |  |  |

| COM34                         | 2*RS232 2*5 pin header          |  |  |

| J_AUD                         | 1*Audio 2*5 pin header          |  |  |

| RST                           | RST connector 1*2 pin wafer     |  |  |

| BAT1                          | Battery connector 1*2 pin wafer |  |  |

| SMB1     | SMBUS, 1*4pin wafer                |  |

|----------|------------------------------------|--|

| BLK1     | Back light connector 1*5 pin wafer |  |

| J_PANEL1 | J-PANEL 2*3 pin header             |  |

| CPU_FAN1 | CPU fan pin header, 1*4pin         |  |

| CMOS     | CMOS 1*3pin switch                 |  |

| P_SATA1  | SATA1 power connector, 1*4 wafer   |  |

| S_SATA1  | SATA1 HDD/SSD connector            |  |

| J_PANEL1 | Front panel signal, 2*3pin header  |  |

| ATX-AT   | ATX-AT 1*3pin switch               |  |

| F_PANEL1 | Front panel signal, 2*5 pin header |  |

| NGFF     | M.2 Type 2230 E-key                |  |

| MPE3     | Mini-PCIe connector                |  |

| PWR_CONN | DC Power connector                 |  |

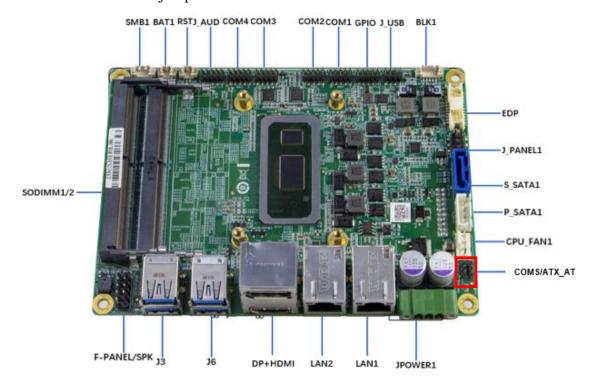

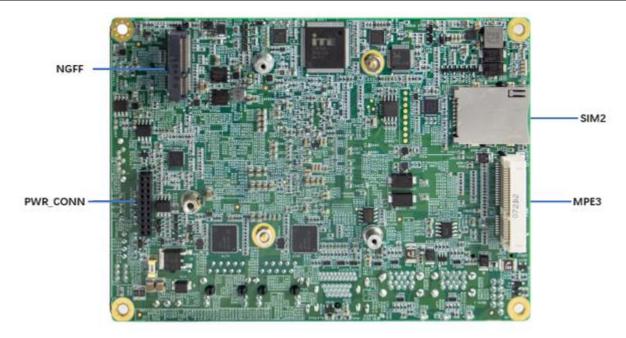

# 2.3 Board layout: Jumper/Switch and Connector Locations

The ECM-I910 Embedded Single Board Computer has a number of jumpers or switches inside the chassis that allows you to configure your system to suit your application. The table below shows the function of each of the board's jumpers:

Figure 2.1 Jumper and Connector Location

Figure 2.2 Jumper and Connector Location

Figure 2.3 I/O Connector

# 2.4 Jumpers and Switches Settings

This section provides instructions on how to configure your motherboard by setting the jumpers and switches. It also includes the motherboard's default settings and your options for each jumper.

# 2.4.1 How to set jumpers and switches

You can configure your motherboard to match the needs of your application by setting the jumpers and switches. A jumper is a metal bridge that closes an electrical circuit. It consists of two metal pins and a small metal clip (often protected by a plastic cover) that slides over the pins to connect them. To "close" (or turn ON) a jumper, you connect the pins with the clip. To "open" (or turn OFF) a jumper, you remove the clip. Sometimes a jumper consists of a set of three pins, labeled 1, 2, and 3. In this case you connect either pins 1 and 2, or 2 and 3. A pair of needle-nose pliers may be useful when setting jumpers.

# **Jumpers and Switches**

Label Function Description

| SW1 Set Power-on mode at AT or ATX |                                             | 3-Pin Switch |

|------------------------------------|---------------------------------------------|--------------|

| COMS                               | Clear CMOS Data Setting                     | 3-Pin Block  |

| J PANEL1                           | LVDS screen 3.3V/5V/12V Power supply Select | 6-Pin Block  |

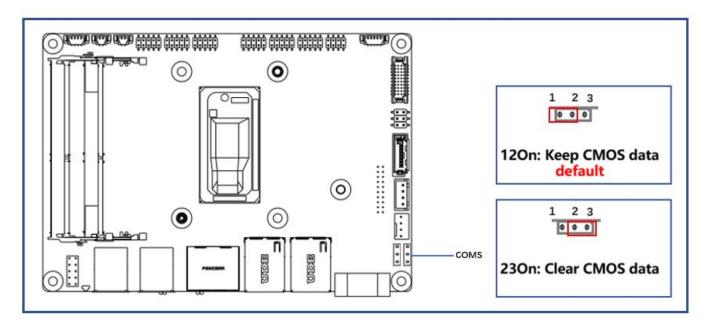

### 2.4.2 COMS-Clear CMOS data

Figure 2.4

The ECM-I910 motherboard contains a switch that can erase CMOS data and reset the system BIOS information. Normally this switch should be set with pins 1-2 closed. If you want to reset the CMOS data, set SW2 to 2-3 closed for just a few seconds, and then move the jumper back to 1-2 closed. This procedure will reset the CMOS to its default setting.

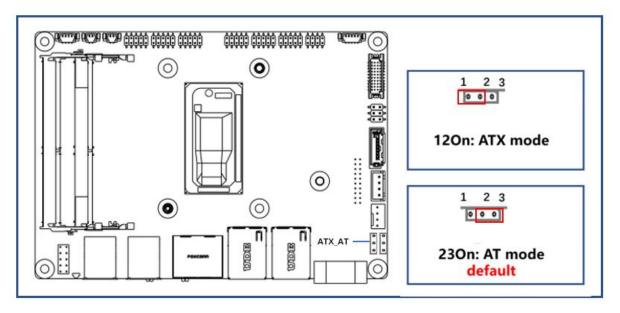

### 2.4.3 SW1-Power on mode AT or ATX selection

Figure 2.5

The ECM-I910 motherboard provides a AT/ATX Switch, which users can set Power-on mode by it. When you dial it at AT, it means power on by AC Power; When you dial it at ATX, it means power on by Power button.

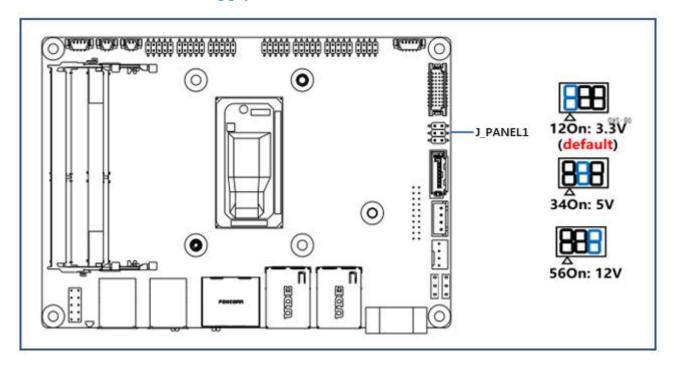

### 2.4.4 J-Panel eDP Power supply 12V/5V/3.3V Mode Select

Figure 2.6

J\_PANEL is used to select the power supplied of LVDS panel.

# 2.5 Install

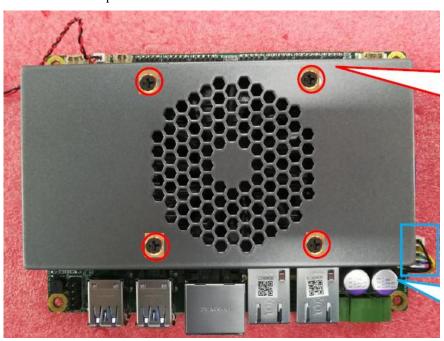

### 2.5.1 Install the radiator

Step 1: Paste the thermal pad with a thickness of 1mm on the CPU as shown in the figure;

Figure 2.7

Step 2: Turn the heat dissipating component over and assemble according to the direction shown in the figure;

Figure 2.8

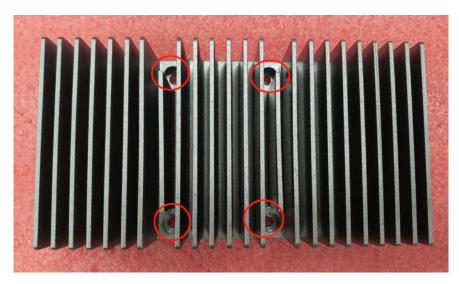

Step 3: Tighten the four CPU screws of the heat sink diagonally in turn;

The following figure 2.9 shows the screw position of the fan radiator, and figure 2.10 shows the screw position of the fanless radiator.

Figure 2.9

Figure 2.10

Step 4: If there is a fan radiator, install the radiator cover and connect the fan cable.

Tighten the four screws circled in the red circle as shown in the figure, and connect the fan wire terminal at the blue circle to connect the line between the capacitor and the heat sink.

Figure 2.11

# I/O Introduction

### 3.1 Introduction

You can access most of the connectors from the top of the board as it is being installed in the chassis. If you have a number of cards installed or have a packed chassis, you may need to partially remove the card to make all the connections.

# 3.2 I/O Introduction and Pin Assignments

This chapter will give the motherboard I/O interfaces introduction and Pin assignments.

### 3.2.1 Ethernet port (LAN1/LA2)

The ECM-I910 is equipped with 2 Intel I210AT Ethernet controllers. The product provides 2\*RJ45, with LED indicators on the front side to show its Active/Link status and Speed status.

Table 3.1 for pin assignments.

Figure 3.1 Ethernet port

| Table 3.1: Ethernet 10/100/1000 Mbps RJ-45 port |                           |     |                           |  |

|-------------------------------------------------|---------------------------|-----|---------------------------|--|

| Pin                                             | 10/100/1000BaseT Signal   | Pin | 10/100/1000BaseT Signal   |  |

| 1                                               | TX+(10/100), LAN_DA+(GHz) | 5   | LAN_DC-(GHz)              |  |

| 2                                               | TX-(10/100), LAN_DA-(GHz) | 6   | RX-(10/100), LAN_DB-(GHz) |  |

| 3                                               | RX+(10/100), LAN_DB+(GHz) | 7   | LAN_DD-(GHz)              |  |

| 4                                               | LAN_DC+(GHz)              | 8   | LAN_DD-(GHz)              |  |

### 3.2.2 USB Connectors (CN4/CN5/CN6)

The ECM-I910 provides up to 6 USB ports, 4\*USB3.0(type A), 2\*USB2.0(pin header), The USB interface can be disabled in the system BIOS setup.

Table 3.2 for USB3.0 pin assignments.

Figure 3.2 USB3.0 type A Connector

| Table 3.2: USB3.0 type A Port Pin Assignments |            |       |             |  |

|-----------------------------------------------|------------|-------|-------------|--|

| Pin                                           | Signal     | Pin   | Signal      |  |

| 1                                             | USB1_VCC   | 6     | StdA_SSRX+  |  |

| 2                                             | D1-        | 7     | GND7        |  |

| 3                                             | D1+        | 8     | StdA_SSTX1- |  |

| 4                                             | GND        | 9     | StdA_SSTX1+ |  |

| 5                                             | StdA_SSRX- | 10    | USB2_VCC    |  |

| 11                                            | USB1_VCC   | 12    | StdA_SSRX+  |  |

| 13                                            | D2-        | 14    | GND13       |  |

| 15                                            | D2+        | 16    | StdA_SSTX2- |  |

| 17                                            | GND16      | 18    | StdA_SSTX2+ |  |

| 5                                             | StdA_SSRX- | Shell | Shield      |  |

Table 3.3 for USB2.0(2\*4pin header) pin assignments.

Figure 3.3 USB2.0 (pin header) connector

| Table 3.3: USB2.0(pin header) pin assignments |           |     |          |  |

|-----------------------------------------------|-----------|-----|----------|--|

| Pin                                           | Signal    | Pin | Signal   |  |

| 1                                             | +V5SB_USB | 5   | USB_z_P8 |  |

| 2                                             | +V5SB_USB | 6   | USB_z_P7 |  |

| 3                                             | USB_z_N8  | 7   | GND      |  |

| 4                                             | USB_z_N7  | 8   | GND      |  |

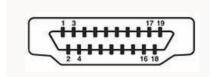

# 3.2.3 HDMI port (HDMI1)

The ECM-I910 provides a high-resolution HDMI display port. They can support the most resolution up to 4096\*2304@24Hz.

Table 3.5 for HDMI pin assignments.

Figure 3.4 HDMI Connector

| Table | Table 3.4: HDMI Pin Assignments |     |         |     |        |  |  |

|-------|---------------------------------|-----|---------|-----|--------|--|--|

| Pin   | Signal                          | Pin | Signal  | Pin | Signal |  |  |

| 1     | DATA2_P                         | 8   | GND     | 15  | SCL    |  |  |

| 2     | GND                             | 9   | DATA0_N | 16  | SDA    |  |  |

| 3     | DATA2_N                         | 10  | CLK_P   | 17  | GND    |  |  |

| 4     | DATA1_P                         | 11  | GND     | 18  | VCC    |  |  |

| 5     | GND                             | 12  | CLK_N   | 19  | DETECT |  |  |

| 6     | DATA1_N                         | 13  | NC      |     |        |  |  |

| 7     | DATA0_P                         | 14  | NC      |     |        |  |  |

# 3.2.4 EDP connector

Figure 3.5 EDP connector

Table 3.6 for EDP connector pin assignments.

| Table 3 | Table 3.5: EDP connector Pin Assignments |     |            |  |  |  |

|---------|------------------------------------------|-----|------------|--|--|--|

| Pin     | Signal                                   | Pin | Signal     |  |  |  |

| 1       | /                                        | 11  | PANEL_TXP1 |  |  |  |

| 2       | /                                        | 12  | PANEL_AUXN |  |  |  |

| 3       | PANEL_TXN0                               | 13  | GND        |  |  |  |

| 4       | PANEL_TXN3                               | 14  | PANEL_AUXP |  |  |  |

| 5       | PANEL_TXP0                               | 15  | PANEL_TXN2 |  |  |  |

| 6       | PANEL_TXP3                               | 16  | GND        |  |  |  |

| 7       | GND                                      | 17  | PANEL_TXP2 |  |  |  |

| 8       | /                                        | 18  | HPD        |  |  |  |

| 9       | PANEL_TXN1                               | 19  | VDD_PANEL  |  |  |  |

| 10      | GND                                      | 20  | VDD_PANEL  |  |  |  |

# 3.2.5 DP connector (DP)

Figure 3.6 DP connector

Table 3.7 for DP connector pin assignments.

| Table 3.6 | Table 3.6: DP connector Pin Assignments |     |         |     |        |  |

|-----------|-----------------------------------------|-----|---------|-----|--------|--|

| Pin       | Signal                                  | Pin | Signal  | Pin | Signal |  |

| 1         | DATA0_P                                 | 8   | GND     | 15  | AUXP   |  |

| 2         | GND                                     | 9   | DATA2_N | 16  | GND    |  |

| 3         | DATA0_N                                 | 10  | DATA3_P | 17  | AUXN   |  |

| 4         | DATA1_P                                 | 11  | GND     | 18  | HPD    |  |

| 5         | GND                                     | 12  | DATA3_N | 19  | GND    |  |

| 6         | DATA1_N                                 | 13  | CTRL    | 20  | PWR    |  |

| 7         | DATA2_P                                 | 14  | GND     |     |        |  |

# 3.2.6 Power Input Connector (CN1)

The ECM-I910 uses a power 1x3PIN 3.81mm phoenix connector that supports up to 60W of power and is a low-power solution. Use a 12V adapter to input voltage and a DC power supply to the outlet. If the voltage used is greater than the recommended voltage, the system will not boot or even damage the motherboard.

Figure 3.7 DC IN

| Table 3.7 DC IN connector pin assignments |           |   |    |  |  |

|-------------------------------------------|-----------|---|----|--|--|

| Pin Signal Pin Signal                     |           |   |    |  |  |

| 1                                         | DC IN 12V | 2 | NC |  |  |

| 3 GND                                     |           |   |    |  |  |

# 3.2.7 CMOS battery connector (BAT1)

Figure 3.8 CMOS battery connector

Table 3.8 for pin assignments.

| Table 3.8: CMOS battery connector pin assignments |  |  |  |  |  |

|---------------------------------------------------|--|--|--|--|--|

| Pin Signal Pin Signal                             |  |  |  |  |  |

| 1 BAT+ 2 GND                                      |  |  |  |  |  |

# 3.2.8 Reset connector (J\_RST1)

Figure 3.9 Reset connector

Table 3.9 for pin assignments.

| Table 3.9 Reset connector pin assignments |  |  |  |  |  |

|-------------------------------------------|--|--|--|--|--|

| Pin Signal Pin Signal                     |  |  |  |  |  |

| 1 SYS_RST# 2 GND                          |  |  |  |  |  |

# 3.2.9 Serial ATA1 (S\_SATA1)

Figure 3.10 Serial ATA1 connector

Table 3.10 for pin assignments.

| Table 3.10: Serial ATA1 pin assignments |        |     |        |  |  |

|-----------------------------------------|--------|-----|--------|--|--|

| Pin                                     | Signal | Pin | Signal |  |  |

| 1                                       | GND    | 5   | RX-    |  |  |

| 2                                       | TX+    | 6   | RX+    |  |  |

| 3                                       | TX-    | 7   | GND    |  |  |

| 4                                       | GND    |     |        |  |  |

# 3.2.10 SATA power connector (P\_SATA1)

Figure 3.11 SATA power connector

Table 3.11 for pin assignments.

| Table 3.11: SATA power connector |        |     |        |  |  |

|----------------------------------|--------|-----|--------|--|--|

| Pin                              | Signal | Pin | Signal |  |  |

| 1                                | 5V     | 3   | GND    |  |  |

| 2                                | GND    | 4   | 12V    |  |  |

# 3.2.11 Front PANEL(F\_PANEL)

Figure 3.12

Table 3.12 for pin assignments.

| Table 3.12: F-PANEL Pin Assignments |          |       |          |  |  |

|-------------------------------------|----------|-------|----------|--|--|

| Pin                                 | Signal   | Pin   | Signal   |  |  |

| 1                                   | HDD_LED+ | 6     | PWRBTN#  |  |  |

| 2                                   | PWR_LED+ | 7     | SYS_RST# |  |  |

| 3                                   | HDD_LED- | 8     | GND      |  |  |

| 4                                   | PWR_LED- | 9     | SPK_OUT- |  |  |

| 5                                   | GND      | Shell | Shield   |  |  |

# 3.2.12 Serial port connector1/2 (COM1/2)

The ECM-I910 provides 2 serial ports of COM1/2 by 2x2\*5pin connectors. COM1/2 can be configured as RS232、RS422 or RS485 by BIOS setup. Table 3.13 for pin assignments.

Figure 3.13 COM1/2 Connector

Table 3.13 for pin assignments.

| Table 3.13: | Table 3.13: COM1/2 Serial Ports Pin Assignments |               |               |  |  |  |

|-------------|-------------------------------------------------|---------------|---------------|--|--|--|

| Pin         | RS-232 Signal                                   | RS-422 Signal | RS-485 Signal |  |  |  |

| 1           | DCD                                             | TX-           | DATA-         |  |  |  |

| 2           | RxD                                             | TX+           | DATA+         |  |  |  |

| 3           | TxD                                             | RX+           | NC            |  |  |  |

| 4           | DTR                                             | RX-           | NC            |  |  |  |

| 5           | GND                                             | GND           | GND           |  |  |  |

| 6           | DSR                                             | NC            | NC            |  |  |  |

| 7           | RTS                                             | NC            | NC            |  |  |  |

| 8           | CTS                                             | NC            | NC            |  |  |  |

| 9           | RI                                              | NC            | NC            |  |  |  |

### 3.2.14 COM3/4 (RS232)

Figure 3.14 COM3/4 Connector

| 表 3.14 COM3/4 Serial Ports Pin Assignments |      |  |  |  |  |

|--------------------------------------------|------|--|--|--|--|

| 管脚                                         | 信号名称 |  |  |  |  |

| 1                                          | DCD  |  |  |  |  |

| 2                                          | RXD  |  |  |  |  |

| 3                                          | TXD  |  |  |  |  |

| 4                                          | DTR  |  |  |  |  |

| 5                                          | GND  |  |  |  |  |

| 6                                          | DSR  |  |  |  |  |

| 7                                          | RTS  |  |  |  |  |

| 8                                          | CTS  |  |  |  |  |

| 9                                          | RI   |  |  |  |  |

| 10                                         | NC   |  |  |  |  |

# 3.2.15 8-bit DIO Connector (GPIO)

The ECM-I910 provides a 8-bit DIO by a 2\*5pin connector. Table 3.16 for pin assignments.

Figure 3.15 8-bit DIO Connector

| Table 3.15: 8-bit DIO Pin Assignments |            |     |            |  |  |

|---------------------------------------|------------|-----|------------|--|--|

| Pine                                  | DIO Signal | Pin | DIO Signal |  |  |

| 1 | +V5_GPIO | 6  | GP76 |

|---|----------|----|------|

| 2 | GP74     | 7  | GP72 |

| 3 | GP70     | 8  | GP77 |

| 4 | GP75     | 9  | GP73 |

| 5 | GP71     | 10 | GND  |

# 3.2.16 J\_AUD

Figure 3.16 J\_AUD

Table 3.16 for Pin assignments.

| Table 3.16: J_AUD Pin Assignments |               |     |              |  |

|-----------------------------------|---------------|-----|--------------|--|

| Pin                               | Signal        | Pin | Signal       |  |

| 1                                 | MCIN1_L       | 6   | NC           |  |

| 2                                 | GND_AUD       | 7   | GND_AUD      |  |

| 3                                 | MCIN1_R       | 8   | FRONT_LINOUT |  |

| 4                                 | FRONTR_LINOUT | 9   | LINE1_L_R    |  |

| 5                                 | LINE1_R-R     | 10  | GND_AUD      |  |

# 3.2.17 SMBUS Connector (SMB1)

Figure 3.17 SMBUS Connector

Table 3.17 for Pin assignments.

| Table 3.17: SMB1 Pin Assignments |                   |   |     |  |  |  |

|----------------------------------|-------------------|---|-----|--|--|--|

| Pin                              | Signal Pin Signal |   |     |  |  |  |

| 1                                | GND               | 2 | DAT |  |  |  |

| 3                                | CLK               | 4 | +V5 |  |  |  |

# 3.2.18 CPU\_FAN1

Figure 3.18 CPU\_FAN1 Connector

| Table 3.18: CPU_FAN1 pin Assignments |                       |   |            |  |  |  |

|--------------------------------------|-----------------------|---|------------|--|--|--|

| Pin                                  | Pin Signal Pin Signal |   |            |  |  |  |

| 1                                    | GND                   | 2 | VCC        |  |  |  |

| 3                                    | Control               | 4 | Tachometer |  |  |  |

# **3.2.19 J\_PANEL1**

Figure 3.19 J\_PANEL1 Connector

| Table 3.19 J_PANEL1 pin Assignments |           |  |  |  |

|-------------------------------------|-----------|--|--|--|

| Pin                                 | Signal    |  |  |  |

| 1                                   | V3.3      |  |  |  |

| 2                                   | VDD PANEL |  |  |  |

| 3                                   | VDD PANEL |  |  |  |

| 4                                   | +V5       |  |  |  |

| 5                                   | +V12      |  |  |  |

| 6                                   | VDD PANEL |  |  |  |

# 3.2.20 J-BLK 5PIN

Figure 3.20 J-BLK Connector

| Table 3.20 J-BLK pin Assignments |        |  |  |  |

|----------------------------------|--------|--|--|--|

| Pin                              | Signal |  |  |  |

| 1                                | 12V    |  |  |  |

| 2                                | GND    |  |  |  |

| 3                                | BLEN   |  |  |  |

| 4                                | BLCTL  |  |  |  |

| 5                                | 5V     |  |  |  |

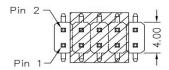

# 3.2.21 M.2 E-Key

Standard M.2 2230 E-Key slot, signal: PCIe, USB, CNVio

Figure 3.21 M.2 E-Key Connector

| Table 3.2.21: M. 2 E-Key 2230 (NGFF2) pin Assignments |               |     |                              |  |

|-------------------------------------------------------|---------------|-----|------------------------------|--|

| Pin                                                   | Signal        | Pin | Signal                       |  |

| 1                                                     | GND           | 2   | +V3.3M2SB                    |  |

| 3                                                     | USB_P5        | 4   | +V3.3M2SB                    |  |

| 5                                                     | USB_N5        | 6   | NC                           |  |

| 7                                                     | GND           | 8   | M.2_BT_PCMCLK                |  |

| 9                                                     | CNV_WR_D1_DN  | 10  | M.2_BT_PCMFRM_CRF_RST_N      |  |

| 11                                                    | CNV_WR_D1_DP  | 12  | M.2_BT_PCMIN                 |  |

| 13                                                    | GND           | 14  | M.2_BT_PCMOUT_CLKREQ         |  |

| 15                                                    | CNV_WR_D0_DN  | 16  | NC                           |  |

| 17                                                    | CNV_WR_D0_DP  | 18  | GND                          |  |

| 19                                                    | GND           | 20  | UART_BT_WAKE_N               |  |

| 21                                                    | CNV_WR_CLK_DN | 22  | M.2_CNV_BRI_DT_BT_UART0_RX   |  |

| 23                                                    | CNV_WR_CLK_DP | 32  | M.2_CNV_RGI_DT_BT_UART0_TX   |  |

| 33                                                    | GND           | 34  | M.2_CNV_RGI_RSP_BT_UART0_CTS |  |

| 35                                                    | PCIE_X4_TX12+ | 36  | M.2_CNV_BRI_DT_BT_UART0_RTS  |  |

| 37                                                    | PCIE_X4_TX12- | 38  | M.2_WLAN_CL_RST_N            |  |

| 39                                                    | GND           | 40  | M.2_WLAN_CL_DATA             |  |

| 41                                                    | PCIE_X4_RX12+ | 42  | M.2_WLAN_CL_CLK              |  |

| 43                                                    | PCIE_X4_RX12- | 44  | DISC_WLAN_WWAN_COEX3         |  |

| 45                                                    | GND           | 46  | DISC_WLAN_WWAN_COEX2         |  |

| 47                                                    | CLK_PCIe_P14  | 48  | DISC_WLAN_WWAN_COEX1         |  |

| 49                                                    | CLK_PCIe_N14  | 50  | SUSCLK                       |  |

| 51                                                    | GND           | 52  | PLTRST_M2_N                  |  |

| 53                                                    | CLK_REQ14#    | 54  | NC                           |  |

| 55                                                    | PCH_WAKE_N    | 56  | NC                           |  |

| 57                                                    | GND           | 58  | NC                           |  |

| 59 | CNV_WT_D1_DN  | 60 | NC                         |

|----|---------------|----|----------------------------|

| 61 | CNV_WT_D1_DP  | 62 | NC                         |

| 63 | GND           | 64 | PULSAR_38P4M_REFCLK        |

| 65 | CNV_WT_D0_DN  | 66 | NC                         |

| 67 | CNV_WT_D0_DP  | 68 | GPPC_B10_CLKREQ5_WIGIG_R_N |

| 69 | GND           | 70 | +V3.3M2SB                  |

| 71 | CNV_WT_CLK_DN | 72 | +V3.3M2SB                  |

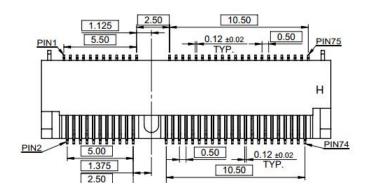

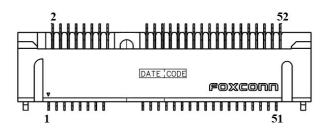

### 3.2.22 1\*Mini-PCle

Signal: PCIe\_L12, Via SATA\_P1, USB2.0\_P6, with SIM1 Slot

Remarks: Automatic detection and switching can be realized through BIOS to realize dual purpose of single slot.

Figure 3.22 Mini-PCIe Connector

| Table Mini PCIe pin Assignments |                |     |                 |  |

|---------------------------------|----------------|-----|-----------------|--|

| Pin                             | Signal         | Pin | Signal          |  |

| 1                               | PCIE_WAKE_N    | 2   | +V3.3_MINICARD2 |  |

| 3                               | NC             | 4   | GND             |  |

| 5                               | NC             | 6   | +V1.5           |  |

| 7                               | CLKREQ#        | 8   | +VUIM_PWR       |  |

| 9                               | GND            | 10  | UIM_DATA        |  |

| 11                              | CLK_MIO1_PCIE- | 12  | UIM_CLK         |  |

| 13                              | CLK_MIO1_PCIE+ | 14  | UIM_RESET       |  |

| 15                              | GND            | 16  | +VUIM_VPP       |  |

| 17                              | NC             | 18  | GND             |  |

| 19                              | NC             | 20  | WIFI2_DISABLE#  |  |

| 21                              | GND            | 22  | PLTRST#         |  |

| 23                              | PCIE_MINI_RX2- | 24  | +V3.3_MINICARD2 |  |

| 25 | PCIE_MINI_RX2+  | 26 | GND             |

|----|-----------------|----|-----------------|

| 27 | GND             | 28 | +V1.5           |

| 29 | GND             | 30 | SMB_SCL_RSM     |

| 31 | PCIE_MINI_TX2-  | 32 | SMB_SDA_RSM     |

| 33 | PCIE_MINI_TX2+  | 34 | GND             |

| 35 | GND             | 36 | USB_D-          |

| 37 | GND             | 38 | USB_D+          |

| 39 | +V3.3_MINICARD2 | 40 | GND             |

| 41 | +V3.3_MINICARD2 | 42 | NC              |

| 43 | GND             | 44 | NC              |

| 45 | NC              | 46 | NC              |

| 47 | NC              | 48 | +V1.5           |

| 49 | NC              | 50 | GND             |

| 51 | NC              | 52 | +V3.3_MINICARD2 |

|    |                 |    |                 |

**BIOS Setup**

# **4.1 BIOS Description**

BIOS is the communication bridge between hardware and software. How to correctly set the BIOS parameters is crucial for the system to work stably and whether the system works at its best.

This chapter describes how to change the system settings through the BIOS settings.

Note: For the purpose of better product maintenance, the manufacture reserves the right to change the BIOS items presented in this manual. The BIOS setup screens shown in this chapter are for reference only and may differ from the actual BIOS.

You need to make SETUP settings as follows:

- 1. An error message appears on the screen during the system self-test and asks for the SETUP setting.

- 2. You want to change the factory default settings based on customer characteristics.

(But in general, customers are not recommended to set it up. In most cases, using the default value is already the best setting.)

The BIOS Setup Utility enables you to configure:

- Hard drives, diskette drives and peripherals

- Video display type and display options

- Password protection from unauthorized use

- Power Management features

# **4.1.1 Entering the Setup Utility**

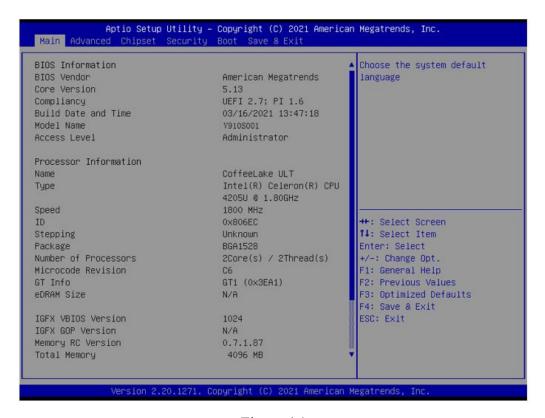

When you power on the system, BIOS enters the Power-On Self-Test (POST) routines. POST is a series of built-in diagnostics performed by the BIOS. After the POST routines are completed, Press the "DEL" key to enter BIOS Setup Utility.

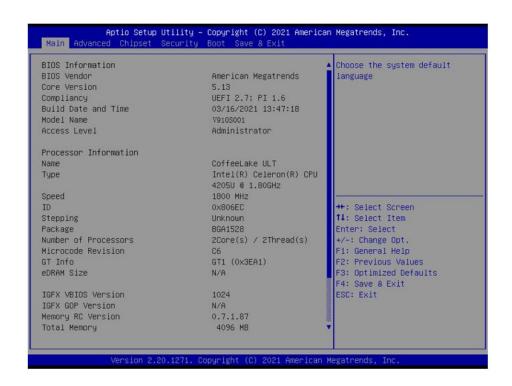

Figure 4.1

# 4.2 BIOS parameter settings

When you start the Setup Utility, the main menu appears. The main menu of the Setup Utility displays a list of the options that are available. A highlight indicates which option is currently selected. Use the cursor arrow keys to move the highlight to other options. When an option is highlighted, execute the option by pressing <Enter>.

Some options lead to pop-up dialog boxes that prompt you to verify that you wish to execute that option. Other options lead to dialog boxes that prompt you for information.

Some options (marked with a triangle ) lead to submenus that enable you to change the values for the option. Use the cursor arrow keys to scroll through the items in the submenu.

In this manual, default values are enclosed in parenthesis. Submenu items are denoted by a triangle .

The default BIOS setting for this motherboard apply for most conditions with optimum performance. We do not suggest users change the default values in the BIOS setup and take no responsibility to any

damage caused by changing the BIOS settings.

# **4.2.1 BIOS Navigation Keys**

Enter the SETUP settings interface, The BIOS navigation keys are listed below:

| Table 3.1: The BIOS navigation keys                  |                                     |

|------------------------------------------------------|-------------------------------------|

| KEY                                                  | FUNCTION                            |

| ESC                                                  | Exit the current menu               |

| $\uparrow \downarrow \longrightarrow \longleftarrow$ | Scrolls through the items on a menu |

| +/-                                                  | Change Opt.                         |

| Enter                                                | Select                              |

| F1                                                   | General Help                        |

| F2                                                   | Previous Values                     |

| F3                                                   | Optimized Defaults                  |

| F4                                                   | Save & Exit                         |

# 4.2.2 Main Menu

When you enter the BIOS Setup program, the main menu appears, giving you an overview of the basic system information. Select an item and press <Enter> to display the submenu.

# Figure 4.2

# **BIOS Vendor (American Megatrends)**

This item shows the information of the BIOS vendor.

# **BIOS ID (0x806EC)**

This item shows the information of the BIOS version.

# OS Selection (Windows 7)

This item shows the OS Selection.

# **Build Date and Time (02/05/2018/19:26:45)**

This item shows the information of the BIOS build date and time.

# **System Date & Time**

The Date and Time items show the current date and time on the computer. If you are running a Windows OS, these items are automatically updated whenever you make changes to the Windows Date and Time Properties utility.

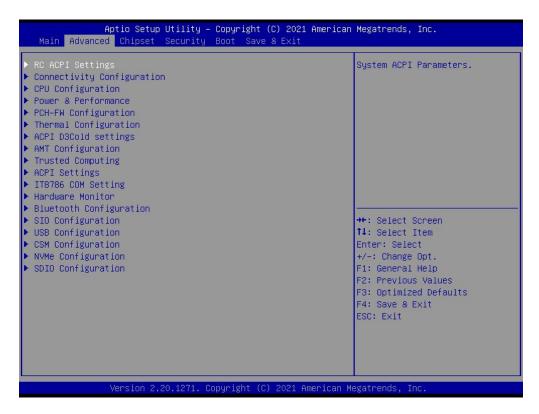

# 4.2.3 Advanced Menu

This page sets up more advanced information about your system. Handle this page with caution. Any changes can affect the operation of your computer.

Figure 4.3

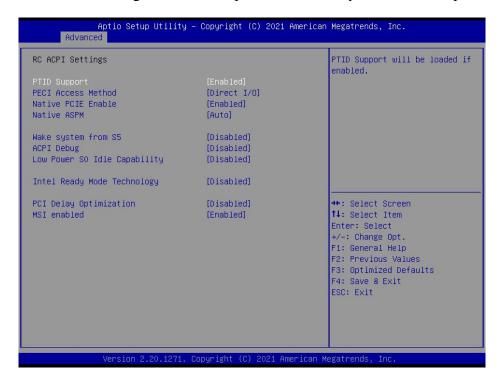

# **ACPI Settings**

The item in the menu shows the highest ACPI sleep state when the system enters suspend.

Figure 4.4

#### **ACPI Sleep State**

Suspend Disabled: Shut down system sleep

## S3: Suspend to RAM

This item allows user to enter the ACPI S3 (Suspend to RAM) Sleep State (default).

Press <Esc> to return to the Advanced Menu page.

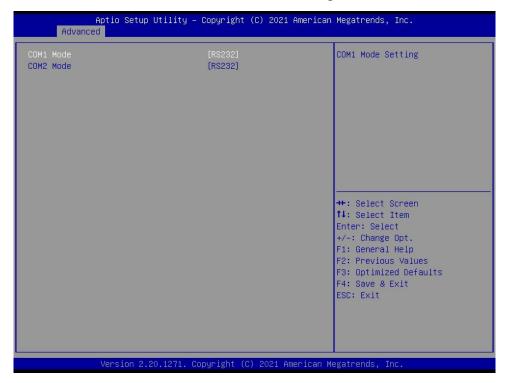

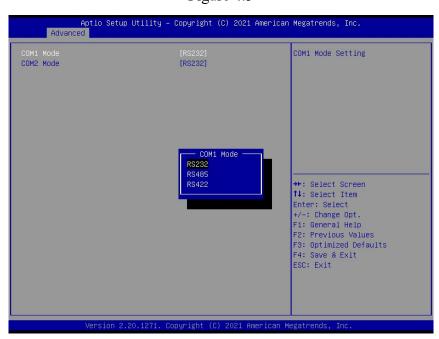

# ► IT8786 Supper IO Configuration

The item in the menu shows the information of RTC wake settings.

Figure 4.5

Figure 4.6

## **Serial Port**

This item is used to set the serial interface to be turned on or off. The setting value is [Enabled]

## [Disabled]

# **Device Setting (Read Only)**

This item displays the interrupt and address of the serial port.

# **Change Setting**

Set port interrupt and address of the serial port.

## **Serial MODE**

Set the mode of the serial port

# H/W Monitor

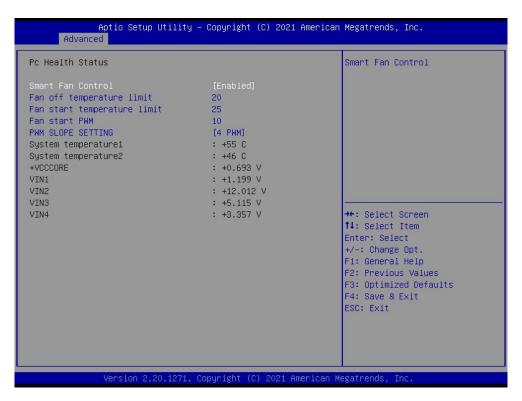

#### **PC Health Status**

This item is used for hardware security detection. The BIOS will display the current CPU and system temperature.

Figure 4.7

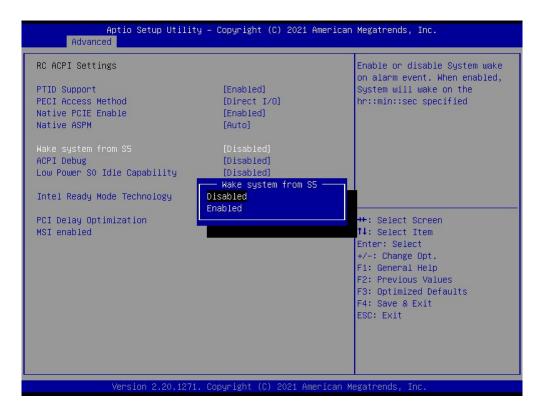

# ► S5 RTC Wake Settings

Figure 4.8

## Wake system from S5

This item is used to set whether to power on regularly. The setting value is [Enabled] [Disabled].

If you select [Enabled], set the hour, minute, and second in the pop-up options.

# **CNVi Presen**

Figure 4.9

#### **CNVi Present**

This is used to set wireless card parameters.

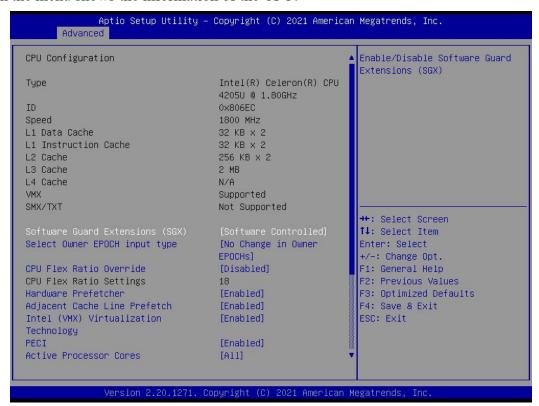

# **►** CPU Configuration

This item in the menu shows the information of the CPU.

Figure 4.10

#### **Socket 0 CPU Information**

This item contains detailed information about the CPU, including the CPU manufacturer, model, frequency, L1 cache size, and L2 cache size.

## **CPU Speed**

This item shows the processor speed.

#### 64-bit

This item shows whether 64-bit operations are supported.

#### **Limit CPUID Maximum**

CPUID refers to CPU information, including model number, CPU family, cache size, clock speed and brand, as well as transistor number, pin type, size, etc. In the BIOS setup options of the Intel platform, it is usually Limit CPUID MAX to 3. The meaning is: limit the execution of the CPUID instruction to

return a value greater than 3. Because return values greater than 3 may cause some operating system wrong, generally set this option to [Disabled] on Windows systems for better overclocking. The default value is [Disabled].

#### **Execute Disabled Bit**

The Execution Disable bit is a hardware feature of the Intel CPU that enables the CPU to avoid certain malicious attacks based on buffer overflow viruses. In addition, the execution of the prohibition bit requires Windows XP SP2, Windows Server 2003 SP1 and other OS to work properly. The implementation principle is that the processor divides several areas in memory, some areas can execute application code, while others do not allow. The setting items are Disabled/Enabled, and the default is Enabled.

# **Intel Virtualization Technology**

Intel Virtualization is the system hypothesis technology used in Intel's CPU. It enables multiple OS to run on a single PC. VT technology will play a very important role in various types of processors (including dual-core processors). This technology enables the processor to have and/or virtualization technology. With Virtualization Technology, we can run two operating systems simultaneously on the same machine.

## **Power Technology**

This item sets the way of Power management.

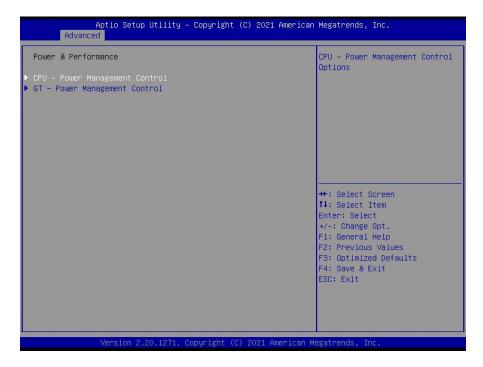

PPM Configuration

Figure 4.11

# **CPU C state Report**

Whether to enable the CPU power status report, the setting values are: [Disabled], [Enabled]. When set to Enabled, the option Max CPU C-state appears and the Max CPU C-state value can be set.

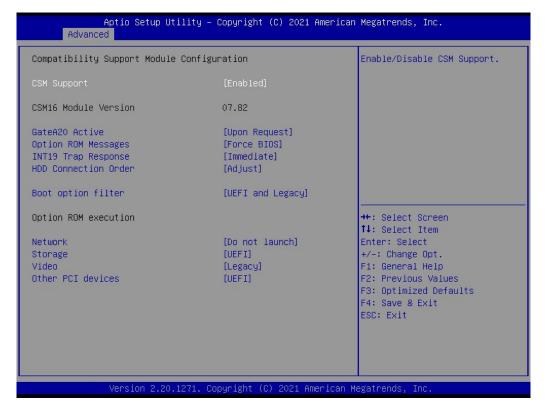

# **CSM Configuration**

Figure 4.12

## **CSM Support**

Compatibility Support Module, which is a compatibility support module, is a special module of UEFI and provides compatibility support for systems that do not support UEFI.

#### **GateA20 Active**

This item indicates whether to disable GA20 through the BIOS server or keep the activation status all the time.

# **Option ROM Messages**

This item shows the display mode of option ROM Message.

## **Boot option filter**

This item indicates the boot priority of controlling EFI or Legacy OpROM.

## **Network**

This item is used to set the EFI network card OpROM boot or the traditional network card OpROM boot or priority boot.

## **Storage**

This item is used to set the EFI storage OpROM boot or the traditional storage OpROM boot.

#### Video

This item is used to set EFI display OpROM startup or traditional display OpROM startup.

#### Other PCI devices

This item is used to set the EFI PCI device OpROM boot or the traditional PCI device OpROM boot

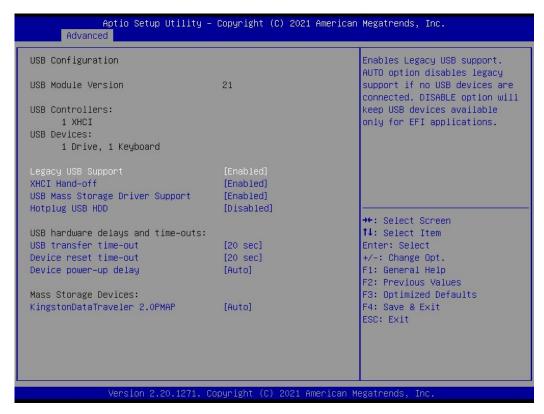

# **USB** Configuration

Use this item to show the information of USB configuration.

Figure 4.13

## **Legacy USB Support**

This item is used to set the USB interface support. If you need to support USB devices under DOS, such as U disk, USB keyboard, etc., set this item to [Enabled] or [Auto]. Otherwise, select [Disabled].

## **USB 2.0 (EHCI) Support**

[Enabled]: Allows USB EHCI transport protocol with a maximum transfer rate of 480Mpbs

[Disabled]: Disable the USB2.0 interface, the traditional transfer rate is 12Mpbs.

## **USB 2.0 Controller Mode**

This item sets USB 2.0 device works in full speed mode (FullSpeed) or high speed mode (HiSpeed).

#### **EHCI Hand-off**

This option is used to determine whether to cut the USB port into USB 2.0 mode before entering the OS.

Set to Disable, It will operate in USB 1.1 compatibility mode before giving ownership to the OS.

## **USB Mass Storage Driver Support**

USB mass storage device support switch.

#### **USB** Transfer time-out

This item Sets the timeout period for control, batch, and interrupt transmission. The default is 20 seconds.

# **Device reset time-out**

This item sets boot command timeout of the large capacity USB disk. The default is 20 seconds.

## **Device Power-up Delay**

This item sets the maximum delay time that the USB device reports to the primary controller.

# **Mass Storage Devices**

This item is used to set the specific type of connected USB device. The setting value is [Auto][Floppy][Forced FDD][Hard Disk][CD-ROM], the default is Auto.

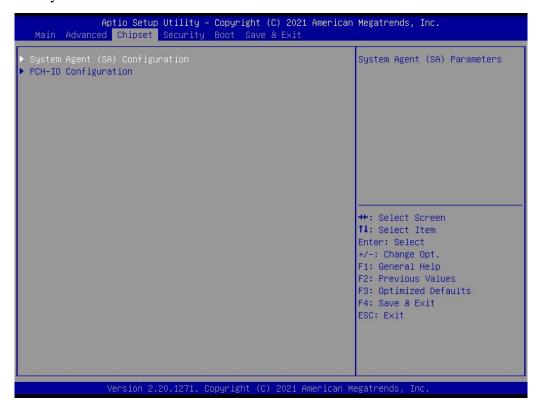

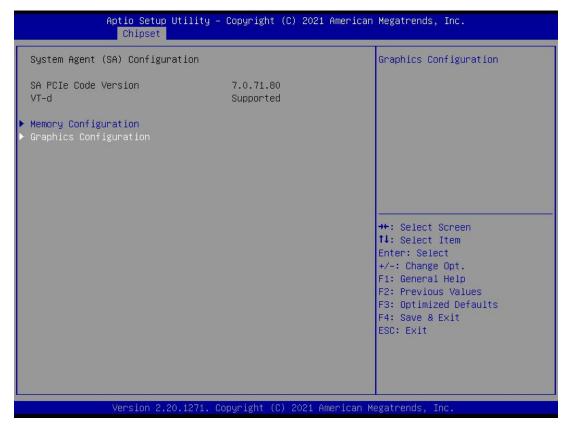

# 4.2.4 Chipset Menu

The chipset menu items allow you to change the settings for the North Bridge chipset, South Bridge chipset and other system.

Figure 4.14

# North Bridge

Scroll to this item and press <Enter> and view the following screen:

Figure 4.15

# **Integrated Graphics Device**

This item indicates whether integrated graphics is enabled.

# **Primary Display**

This item shows the main output display device when the system starts up.

# **DVMT pre-Allocated**

This item sets the memory size pre-assigned to the motherboard integrated graphics in DVMT mode.

#### **DVMT Total Gfx Mem**

This item shows how much dynamic memory is allocated to the integrated graphic in total.

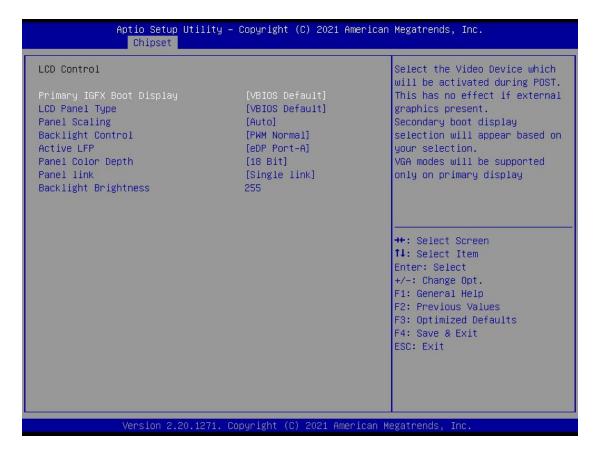

## **LCD Control**

Figure 4.16

# **Primary IGFX Boot Display**

This item sets IGFX main display device on POST stage, not affected by external graphics card, options are LVDS, CRT, HDMI. It defaults by VBIOS.

## **Secondary IGFX Boot Display**

This item sets IGFX second display device on POST stage.

## **LCD Panel Type**

This item sets resolution of the motherboard LVDS screen.

Press <Esc> to return to the Chipset Menu page.

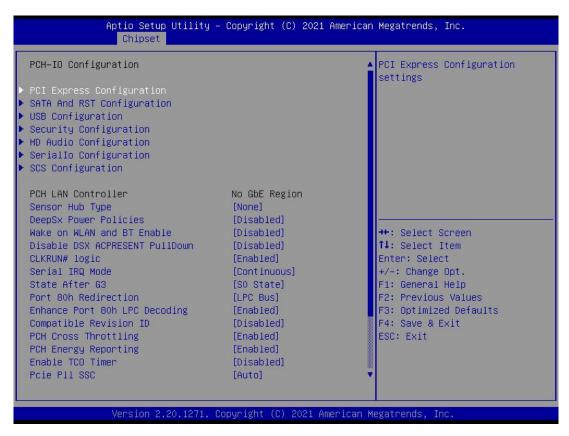

# South Bridge

Scroll to this item and press <Enter> and view the following screen:

Figure 4.17

#### **Restore AC Power Loss**

This item sets the power-on status after power-on. If Power Off is selected, you need to press the power button to power on after power-on. If Power On is selected, it will be powered on directly after power-on. If Last State is selected after power-on, it will be restored to the state before power-off. order to use this feature.

Press <Esc> to return to the Chipset Menu page.

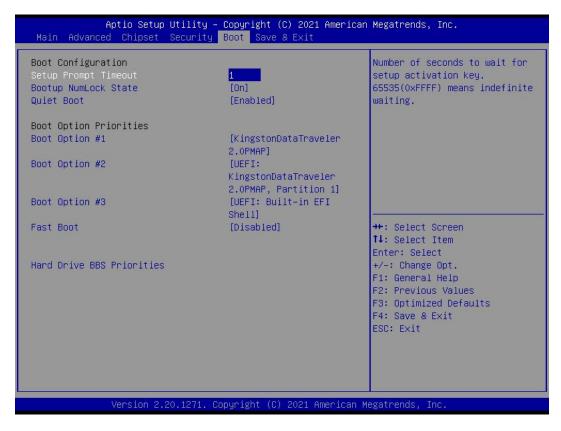

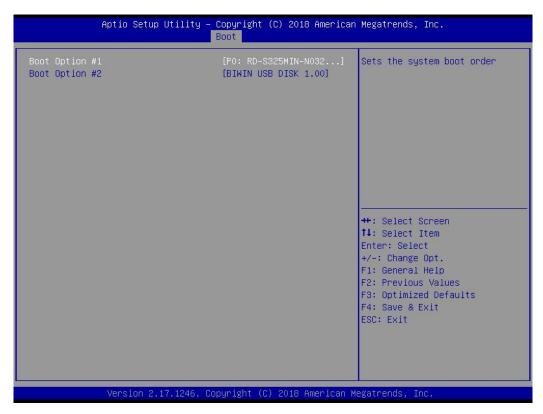

## 4.2.5 Boot Menu

This page enables you to set the keyboard NumLock state and devices boot sequence.

Figure 4.18

## **Setup Prompt Timeout**

This item sets the wait time for the Setup shortcut. If you do not press the Setup shortcut within the set time, it will continue to boot.

#### **Bootup Numlock State**

This item determines if the NumLock key is active or inactive at system start-up time. The default value is On, which is a digital lock on when the system starts. Set to Off, the keypad is in cursor control state at startup.

## **Show Full Logo**

This item shows the vendor logo on the startup screen.

[Enabled]: Display static LOGO screen at startup;

[Disabled]: Display self-test information at start.

# **Boot Option #1/#2**

These items show the boot priorities.

#1 is the highest priority boot device in the boot option.

#### **Hard Drive BBS Priorities**

Figure 4.19

This item sets the hard disk that can be used as the boot device. If there are multiple hard disks, you should select the priority of these hard disks in the item. The highest priority hard disk will be displayed in Boot Option #1.

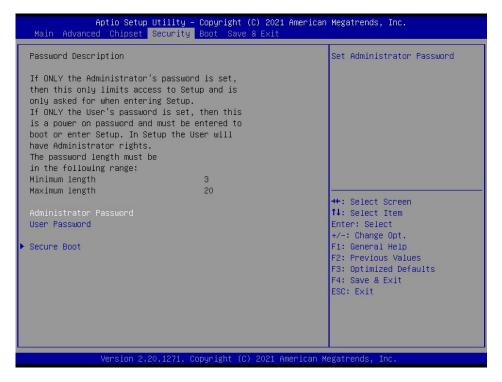

# 4.2.6 Security Menu

Scroll to this item and press <Enter> and view the following screen:

Figure 4.20

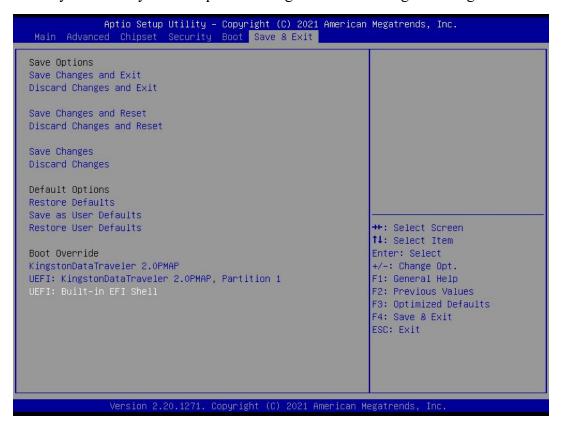

## 4.2.7 Save & Exit Menu

This page enables you to exit system setup after saving or without saving the changes.

Figure 4.21

## **Save Changes and Exit**

This item enables you to save the changes that you have made and exit.

## **Discard Changes and Exit**

This item enables you to discard any changes that you have made and exit.

## **Restore Defaults**

This item enables you to restore the system defaults.

# 4.3 Updating the BIOS

The BIOS (Basic Input and Output System) Setup Utility displays the system's configuration status and provides you with options to set system parameters. The parameters are stored in battery-backed-up

CMOS RAM that saves this information when the power is turned off. When the system is turned back on, the system is configured with the values you stored in CMOS.

The BIOS provides the underlying driver for hardware resources and is the bridge between hardware and operating system. Now hardware and various applications are constantly updated. When your system encounters problems, such as the system does not support the latest published CPU, you need to upgrade your BIOS.

## NOTE:

- 1. Only upgrade the BIOS if you encounter problems and need to.

- 2. To upgrade the BIOS, please use the BIOS read/write program attached to our driver CD or download the updated version of the program from the relevant website.

- 3. Do not turn off the power or reboot the system during the upgrade process, so your BIOS data will be damaged and the system may not boot.

- 4. After the refresh is complete, you need to manually optimize the LOAD Default.

- 5. To prevent accidents, please backup the current BIOS data first.

**CHAPTER**

**SYSTEM RESOURCE**

# 5.1 WDT and GPIO

| 5.1.1 | <b>WDT</b> |

|-------|------------|

| 0.1.1 | 1122       |

| / <b>*</b> = |                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------|

| 1            | * void jhctech_init();                                                                           |

| 2            | * function description: library initializated, This function must be called before calling other |

| fun          | ctions                                                                                           |

| 3            | * parameter description:                                                                         |

| 4            | * creation date:                                                                                 |

| 5            | *                                                                                                |

|              | */                                                                                               |

|              |                                                                                                  |

| voi          | d jhctech_init();                                                                                |

| / <b>*</b> = | <del></del>                                                                                      |

| 1            | * void jhctech_init();                                                                           |

| 2            | * function description: library release, Pair with jhctech_init, release the library's occupied  |

| resc         | ources when not needed                                                                           |

| 3            | * parameter description:                                                                         |

| 4            | * creation date:                                                                                 |

| 5            | *                                                                                                |

| ===          | */                                                                                               |

| voi          | d jhctech_deinit();                                                                              |

| / <b>*</b> = |                                                                                                  |

|              |                                                                                                  |

|              |                                                                                                  |

| 5.1.         | 2 GPIO                                                                                           |

| / <b>*</b> = |                                                                                                  |

| 1            | * BYTE I910_MB_gpio_input(WORD port)                                                             |

| 2            | * function description: read the motherboard GPIO input level                                    |

| 3            | * parameter description:                                                                         |

Return value: Return a byte (8 bit), each bit of the 8 bit corresponding to the level state of a GPIO pin.

| Return | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|--------|------|------|------|------|------|------|------|------|

| value  |      |      |      |      |      |      |      |      |

|        |      |      |      |      |      |      |      |      |

| GPIO   | PIN8 | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 |

| pin    |      |      |      |      |      |      |      |      |

|        |      |      |      |      |      |      |      |      |

parameter: Port Fill in the motherboard GPIO port, which is a fixed value designed by the manufacturer

| 4  | * creation date:                  |     |

|----|-----------------------------------|-----|

| 5  |                                   | *   |

|    |                                   | =*/ |

| BY | ΓΕ I910 MB gpio input(WORD port); |     |

- 1 \* void I910\_MB\_gpio\_output(WORD port, BYTE value);

- 2 \* function description: high and low level output of the motherboard

- 3 \* parameter description:

parameter:

Port Fill in the motherboard GPIO port, which is a fixed value designed by the manufacturer

Value 8 bits of a byte, each bit controls a GPIO pin output value

Bit =1, means output high level

Bit =0, means output low level

| value    | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|----------|------|------|------|------|------|------|------|------|

| GPIO pin | PIN8 | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 |

| 4            | * creation date:                                                                                |     |

|--------------|-------------------------------------------------------------------------------------------------|-----|

| 5            | *                                                                                               |     |

| =            | */void I910_MB_gpio_output(WORD port,BYTE value);                                               | ,   |

| /* <u>-</u>  |                                                                                                 |     |

| 1            | * void I910_MB_gpio_init();                                                                     |     |

| 2<br>use     | * function description: Motherboard gpio initialization function, need to be called once before | ore |

| 3            | * parameter description:                                                                        |     |

| 4            | * creation date:                                                                                |     |

| 5 *          | *                                                                                               | /   |

| V            | oid I910_MB_gpio_init();                                                                        |     |

| voi          | id I910_MB_gpio_init();                                                                         |     |

| / <b>*</b> = |                                                                                                 |     |

| 1            | * void I910_watchdog_set(int time);                                                             |     |

\* function description: WDT function 2 \* parameter: Time sets the dog feed time, the time value is 0-255, 3 Setting 0 means to turn off the watchdog \* creation date: 4 5 void I910 watchdog set(int time); \* void I910 2nd gpio mode(int port,int mode); 1 \* function description: subcard input and output mode settings 2 \* parameter description: 3 parameter: port fill in GPIO number, 1 or 2 mode 8 bits of a byte, each bit controls input and output mode of a GPIO pin bit = 1, Corresponding pin as input bit = 0, Corresponding pin as output

| mode     | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2     | Bit1 | Bit0 |

|----------|------|------|------|------|------|----------|------|------|

| GPIO pin | PIN8 | PIN7 | PIN6 | PIN5 | PIN4 | PIN<br>3 | PIN2 | PIN1 |

Note: The output value is valid only when the pin is in output mode.

| 4            | * creation date:  |             |                        |            |           |            |           |            |      |       |

|--------------|-------------------|-------------|------------------------|------------|-----------|------------|-----------|------------|------|-------|

| 5            |                   |             |                        |            |           |            |           |            |      | *     |

| ====<br>void | 1 I910_2nd_gpio_  | mode(int    | port,int m             | node);     |           |            |           |            |      | ===*/ |

| 1            | * void I910_2nd   | _gpio_ou    | tput(int po            | ort,int le | vel);     |            |           |            |      |       |

| 2            | * function descri | ption: sı   | ibcard out             | put high   | and low   | level      |           |            |      |       |

| 3            | *parameter desc   | irption:    |                        |            |           |            |           |            |      |       |

|              | parameter:        | port fill i | n GPIO n               | umber o    | f the sub | card, 1 or | r 2       |            |      |       |

|              |                   | level 8 b   | its of a by            | rte, each  | bit contr | ols a GP   | lO pin ou | ıtput valu | e,   |       |

|              |                   | Bit =1, r   | neans outp             | out high   | level     |            |           |            |      |       |

|              |                   | Bit =0, r   | neans out <sub>l</sub> | out low l  | evel      |            |           |            |      |       |

|              | level             | Bit7        | Bit6                   | Bit5       | Bit4      | Bit3       | Bit2      | Bit1       | Bit0 |       |

|              | GPIO pin          | PIN8        | PIN7                   | PIN6       | PIN5      | PIN4       | PIN3      | PIN2       | PIN1 |       |

| level    | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|----------|------|------|------|------|------|------|------|------|

| GPIO pin | PIN8 | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 |

description: The output value is valid only when the pin is in output mod

| 4 | * creation date: |              |

|---|------------------|--------------|

| 5 |                  | *            |

|   |                  | = <b>*</b> / |

void I910 2nd gpio output(int port,int level);

/\*-----

- 1 \* int I910 2nd gpio input(int port);

- 2 \* function description: read the motherboard GPIO input level

- 3 \* parameter description:

Return value: return a byte (8 bit), each bit of the 8 bit corresponding to the level state of a GPIO pin

Value=1, means high level

Value=0, means low level

| Return value | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|--------------|------|------|------|------|------|------|------|------|

| GPIO pin     | PIN8 | PIN7 | PIN6 | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 |

parameter: port fill in subcard GPIO number, 1 or 2

descripiton: The read value is valid only when the pin is in input mode

4 \* creation date:

5

**\_\_\_\_\_\***/

int I910\_2nd\_gpio\_input(int port);